### INTEGRATED CIRCUITS

Product specification Supersedes data of 2002 Dec 09 2004 Jan 26

### CONTENTS

| 1          | FEATURES                                           | 8.1<br>8.2   | Initialization of boundary scan circuit<br>Device identification codes |

|------------|----------------------------------------------------|--------------|------------------------------------------------------------------------|

| 1.1<br>1.2 | Video input and preprocessing<br>Video compression | 9            | I <sup>2</sup> C-BUS CONTROL AND STATUS<br>REGISTERS                   |

| 1.3<br>1.4 | Audio input<br>Audio compression                   | 10           | LIMITING VALUES                                                        |

| 1.4        | Stream multiplexer                                 | 11           | THERMAL CHARACTERISTICS                                                |

| 1.6        | Output interface                                   | 12           | CHARACTERISTICS                                                        |

| 1.7        | Control domain                                     |              |                                                                        |

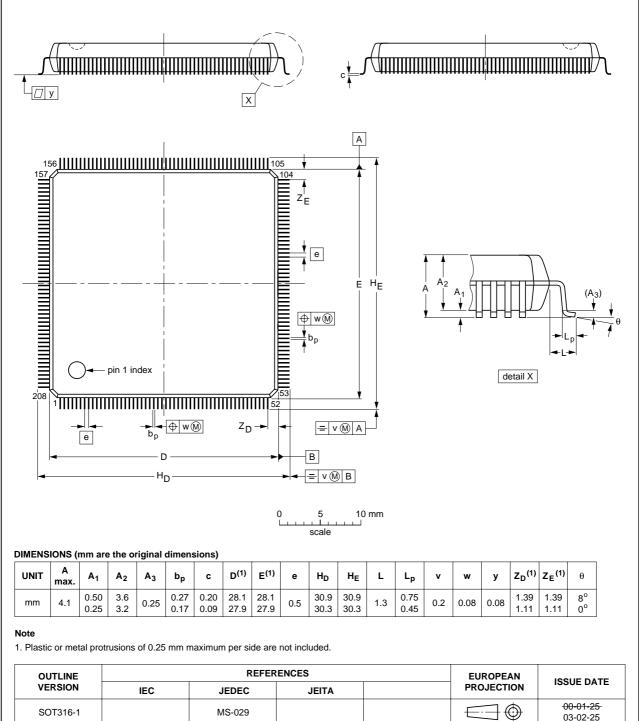

| 1.8        | Other features                                     | 13           | PACKAGE OUTLINE                                                        |

| 2          | GENERAL DESCRIPTION                                | 14           | SOLDERING                                                              |

| 2.1        | General                                            | 14.1         | Introduction to soldering surface mount                                |

| 2.2        | Application fields                                 | 44.0         | packages                                                               |

| 3          | QUICK REFERENCE DATA                               | 14.2<br>14.3 | Reflow soldering<br>Wave soldering                                     |

| 4          | ORDERING INFORMATION                               | 14.3         | Manual soldering                                                       |

| 5          | BLOCK DIAGRAM                                      | 14.5         | Suitability of surface mount IC packages for                           |

| 6          | PINNING                                            |              | wave and reflow soldering methods                                      |

| -          |                                                    | 15           | DATA SHEET STATUS                                                      |

| 7          | FUNCTIONAL DESCRIPTION                             | 16           | DEFINITIONS                                                            |

| 7.1        | System operation                                   | 17           | DISCLAIMERS                                                            |

| 7.2<br>7.3 | Digital video input                                |              |                                                                        |

| 7.3<br>7.4 | Video compression<br>Digital audio input           | 18           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENT                         |

| 7.5        | Audio compression                                  |              |                                                                        |

| 7.6        | SDRAM interface                                    |              |                                                                        |

| 7.7        | Multiplexer                                        |              |                                                                        |

| 7.8        | MPEG stream output port                            |              |                                                                        |

| 7.9        | Clock generation                                   |              |                                                                        |

| 7.10       | Power control and reset                            |              |                                                                        |

| 7.11       | I <sup>2</sup> C-bus interface                     |              |                                                                        |

8

**Product specification**

### **SAA6752HS**

I<sup>2</sup>C COMPONENTS

BOUNDARY SCAN TEST

7.12

Exception handling

### **1 FEATURES**

### 1.1 Video input and preprocessing

- Digital YUV input according to "ITU-R BT.656" (8 bits at 27 MHz) and "ITU-R BT.601"

- Support of enhanced *"ITU-R BT.656"* input format containing decoded VBI data readable via I<sup>2</sup>C-bus; Closed Caption (CC), Wide Screen Signalling (WSS) and copyright information with Copy Generation Management System (CGMS)

- Processing of non-broadcast video signals from analog VCR according to IEC 756

- Two video clock input pins for switching two digital video sources

- *"ITU-R BT.601"* format conversion to 1/2D1, 2/3D1 and Standard Interchange Format (SIF)

- 4:2:2 to 4:2:0 colour format conversion

- Decimation filtering for all format conversions

- Adaptive median filter and motion compensated filter for input noise reduction.

#### 1.2 Video compression

- Real-time MPEG-2 encoding compliant to Main Profile at Main Level (MP@ML) for 625 and 525 interlaced line systems

- Supported resolutions: D1, 2/3D1, 1/2D1 and SIF

- IPB frame, IP frame and I frame only encoding supported at all modes

- Supported bit rates: up to 25 Mbit/s I-only encoding; up to 15 Mbit/s IP-only or IBP encoding.

- Variable video bit rate mode for constant picture quality and constant bit rate mode to gain optimum picture quality from a fixed channel transfer rate

- Access to bit rate control parameters whilst encoding to support external real-time control algorithms (e.g. constrained variable bit rate control)

- Programmable Group Of Pictures (GOP) structure

- · Innovative motion estimation with wide search range

- Adaptive quantization

- Motion compensated noise filter.

### 1.3 Audio input

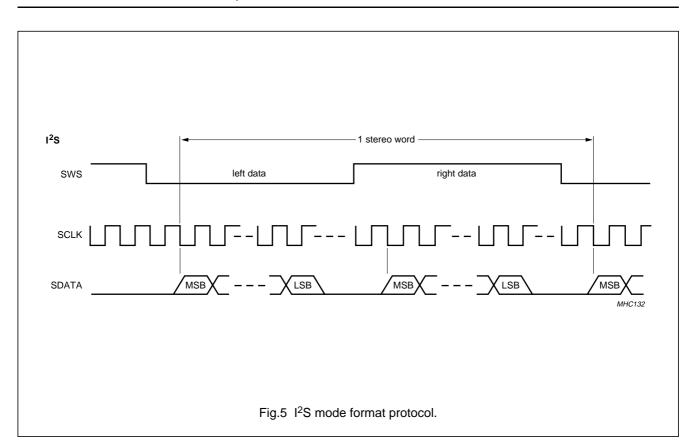

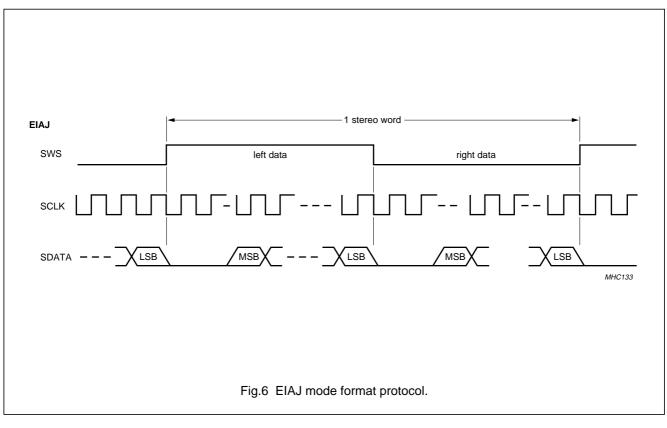

- Audio inputs: I<sup>2</sup>S format or EIAJ format (16, 18 or 20 bits), master or slave mode at 32, 44.1 and 48 kHz

- Two digital I<sup>2</sup>S input ports for selection between two digital audio sources

- Audio clock generation: 256f<sub>s</sub> or 384f<sub>s</sub> (where f<sub>s</sub> = 48 kHz) locked to video frame rate (if video is present and locking is enabled)

- Sample rate conversion to 48 kHz (locked to video frame rate if enabled) for slave mode operation in all modes except Digital Versatile Disc (DVD) compliant bypass.

### 1.4 Audio compression

- Dolby<sup>®(1)</sup> Digital Consumer Encoding (DDCE) also known as AC-3<sup>(2)</sup> 2 channel audio encoding at 256 kbit/s or 384 kbit/s (only for SAA6752HS/V103)

- MPEG-1 layer 2 audio encoding at 256 kbit/s or 384 kbit/s

- Input data bypass for Linear Pulse Code Modulation (LPCM) and compressed audio data [MPEG-1, MPEG-2, Dolby<sup>®</sup> Digital (DD) and Digital Theatre System (DTS)] according to IEC 61937

- Preamble Pc, Preamble Pd and bit stream information captured for identification of modes during bypass of compressed audio data for MPEG-1, MPEG-2, DD and DTS according to IEC 61937

- Audio mute via l<sup>2</sup>C-bus control for all modes except DVD-compliant bypass.

(2) AC-3 is a registered trademark of Dolby Laboratories Licensing Corporation.

<sup>(1)</sup> Dolby is a registered trademark of Dolby Laboratories Licensing Corporation.

## MPEG-2 video and MPEG-audio/AC-3

# audio encoder with multiplexer

### SAA6752HS

### 1.5 Stream multiplexer

- Multiplexing of video and audio streams according to the MPEG-2 systems standard (*"ISO 13818-1"*)

- Generation and output of MPEG-2 Transport Streams (TS), MPEG-2 Program Streams (PS), Packetized Elementary Streams (PES) and Elementary Streams (ES) compliant to the DVD, D-VHS and DVB standards

- MPEG time stamp (PTS/DTS/SCR/PCR) generation and insertion (synchronization)

- · Insertion of metadata

- Optional generation of empty time slots for subsequent insertion of application specific data packets

- Optional insertion of user data in the GOP header and in the picture header

- Optional automatic insertion of Closed Caption data according to DVD or ATSC standard

- Optional generation of transport streams with variable bit rate.

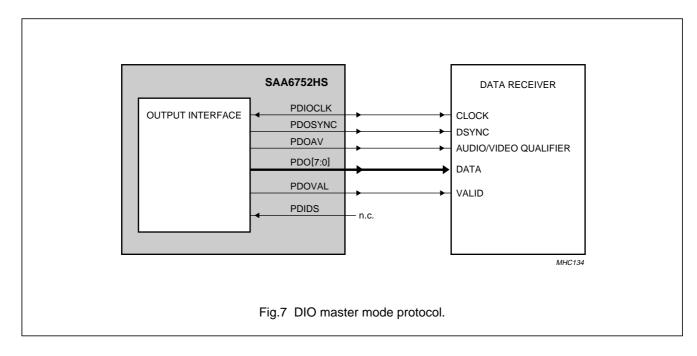

### 1.6 Output interface

- Parallel interface 8-bit master/slave output

- 3-state output port

- Glueless interfacing with IEEE 1394 chip sets (for example, PDI 1394 L11)

- Data Expansion Bus Interface (DEBI) interface.

### 1.7 Control domain

- All control done via I<sup>2</sup>C-bus

- I<sup>2</sup>C-bus slave transceiver up to 400 kbit/s

- I<sup>2</sup>C-bus slave address select pin

- Host interrupt flag pin.

### 1.8 Other features

- Single external clock or single crystal 27 MHz

- Separate 27 MHz system clock output

- Interface voltage 3.3 V

- TTL compatible digital outputs

- Power supply voltage 3.3 and 2.5 V

- Boundary Scan Test (BST) supported

- Power-down mode

- Single SDRAM system memory (16 Mbit@16 bit or 64 Mbit@16 bit).

### 2 GENERAL DESCRIPTION

### 2.1 General

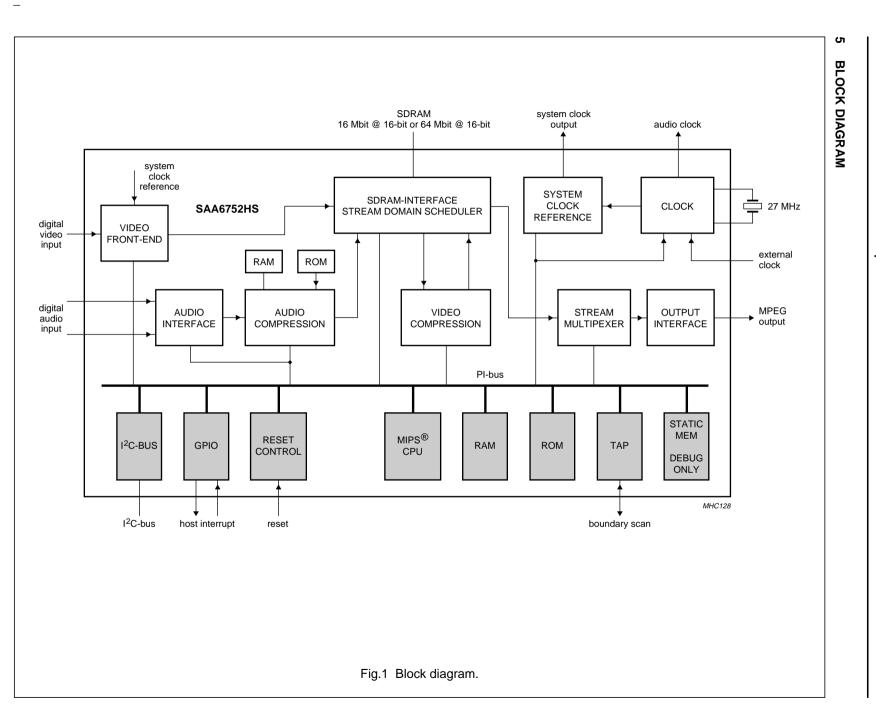

Philips Semiconductors' second generation real time MPEG-2 encoder, the SAA6752HS, is a highly integrated single-chip audio and video encoding solution with flexible multiplexing functionality. With our expertise in two critical areas for consumer video encoding, noise filtering and motion estimation, we have pushed the boundaries for video quality even further, providing enhanced quality for low bit rates and enabling increased recording times for a given storage capacity. The SAA6752HS will also enable a key driver for new consumer digital recording applications and system cost reduction. By integrating all audio encoding and multiplexing functionality we will be moving from a three chip to a one chip system, with cost efficient design and process technology, thus providing a truly low cost, high quality encoding system.

The SAA6752HS/V104 is intended for customers whose application does not require the DDCE function.

The SAA6752HS gives significant advantages to customers developing digital recording applications:

- Fast time-to-market and low development resources. By adding a simple external video input processor IC, an audio analog-to-digital converter, and an external SDRAM, analog video and audio sources are compressed into high quality MPEG-2 video and MPEG-1 layer 2 or AC-3 audio streams, multiplexed into a single program or transport stream for simple connection to various storage media or broadcast media. Hence, making design effort for our customers a minimum, as well as removing the need for in-depth experience in MPEG encoding.

- Low system host resources. All video and audio encoding algorithms and software are run on an internal MIPS<sup>®(1)</sup> processor. The SAA6752HS only requires a small amount of communication from the system host processor to set up and control required encoding parameters via the l<sup>2</sup>C-bus.

<sup>(1)</sup> MIPS is a registered trademark of MIPS Technologies.

### 2.2 Application fields

### 2.2.1 DVD BASED OPTICAL DISC RECORDERS (DVD+RW, DVD-RW, DVD-RAM)

Emerging optical disc based recording systems target to replace the existing consumer recording (VCR) and playback (DVD and VCD) products. The first generation recordable DVD based products will want to maximise recording times for the 4.7 Gbyte storage capacity. For these systems the SAA6752HS is critical, with its superior noise filtering and motion estimation, in enabling high quality at low bit rates.

Playback compatibility with existing DVD decoding solutions will also be important, which is why the SAA6752HS provides Dolby<sup>®</sup> digital consumer (AC-3) audio encoding to allow playback through existing players implementing DDCE (AC-3) decoding dominant in current DVD platforms.

The DVD stream is based on MPEG Program Stream (PS). The SAA6752HS directly outputs MPEG PS compliant to the DVD standard.

### 2.2.2 HDD BASED TIME SHIFT RECORDING

Hard Disc Drive (HDD) based time-shift systems enable Personalized TV (PTV) functionality, providing consumers with new powers of control over what and when to watch broadcast content. With the audio and video content recorded digitally, identification, search and retrieval becomes a 'no brainer' task as compared to traditional VCR functionality. Combine this with electronic program guides and intelligent control, and the PTV can also analyse the viewers watching habits to search for programs likely to be of interest and automatically recorded in anticipation of the viewers preferences.

Since HDD recorders are closed systems, the recording format stream can be proprietary. The SAA6752HS flexible multiplexing formats support a number of recording stream formats for HDD including MPEG Transport Stream (TS) or MPEG Packetized Elementary Stream (PES).

### 2.2.3 DIGITAL VCR (DVHS) RECORDING

A DVHS player records streams based on MPEG Transport Streams (TS) packed in logical tape tracks. The SAA6752HS output streams are compliant with DVHS standard requirements.

#### 2.2.4 VIDEO EDITING/TRANSMISSION/SURVEILLANCE/ CONFERENCING

The SAA6752HS can operate as a stand-alone device in all the above applications. The SAA6752HS full features and flexibility allows customers to tailor functionality and performance to specific application requirements. All required control settings such as GOP size and bit rate modes can be selected via the I<sup>2</sup>C-bus.

### 3 QUICK REFERENCE DATA

| SYMBOL               | PARAMETER                                    | MIN.                                   | TYP. | MAX.                                   | UNIT   |

|----------------------|----------------------------------------------|----------------------------------------|------|----------------------------------------|--------|

| V <sub>DDP</sub>     | digital supply voltage (pad cells)           | 3.0                                    | 3.3  | 3.6                                    | V      |

| V <sub>DDCO</sub>    | digital supply voltage (core)                | 2.3                                    | 2.5  | 2.7                                    | V      |

| V <sub>DDA</sub>     | analog supply voltage (oscillator and PLL)   | 2.3                                    | 2.5  | 2.7                                    | V      |

| I <sub>DD(tot)</sub> | total analog plus digital supply current     | 407                                    | 453  | 525                                    | mA     |

| P <sub>tot</sub>     | total power dissipation                      | 0.95                                   | 1.16 | 1.48                                   | W      |

| f <sub>DCXO</sub>    | quartz frequency (digital controlled tuning) | $27 \times [1 - (200 \times 10^{-6})]$ | 27   | $27 \times [1 + (200 \times 10^{-6})]$ | MHz    |

| f <sub>SDRAM</sub>   | SDRAM clock frequency                        | -                                      | 108  | -                                      | MHz    |

| f <sub>SCL</sub>     | I <sup>2</sup> C-bus input clock frequency   | 100                                    | _    | 400                                    | kHz    |

| В                    | output bit-rate                              | 1.5                                    | _    | 25                                     | Mbit/s |

| V <sub>IH</sub>      | HIGH-level digital input voltage             | 1.7                                    | _    | 3.6                                    | V      |

| V <sub>IL</sub>      | LOW-level digital input voltage              | -0.5                                   | _    | +0.7                                   | V      |

| V <sub>OH</sub>      | HIGH-level digital output voltage            | V <sub>DDP</sub> – 0.4                 | _    | V <sub>DDP</sub>                       | V      |

| V <sub>OL</sub>      | LOW-level digital output voltage             | 0                                      | _    | 0.4                                    | V      |

| T <sub>amb</sub>     | ambient temperature                          | 0                                      | _    | 70                                     | °C     |

### 4 ORDERING INFORMATION

| TYPE NUMBER                      |                     | PACKAGE                                                  |          |  |  |  |  |

|----------------------------------|---------------------|----------------------------------------------------------|----------|--|--|--|--|

| ITPE NUMBER                      | NAME DESCRIPTION VE |                                                          |          |  |  |  |  |

| SAA6752HS/V103 <sup>(1)(3)</sup> |                     |                                                          | SOT316-1 |  |  |  |  |

| SAA6752HS/V104 <sup>(2)(4)</sup> |                     | body $28 \times 28 \times 3.4$ mm; high stand-off height |          |  |  |  |  |

### Notes

- 1. MPEG-2 video and MPEG-audio/AC-3 audio encoder with multiplexer.

- 2. MPEG-2 video and MPEG-audio encoder with multiplexer, but without AC-3 audio encoder.

- 3. SAA6752HS/V103 is a replacement of SAA6752HS/V101 with enhanced functionality.

- 4. SAA6752HS/V104 is a replacement of SAA6752HS/V102 with enhanced functionality.

Philips Semiconductors

Product specification

# audio encoder with multiplexer MPEG-2 video and MPEG-audio/AC-3

SAA6752HS

2004 Jan 26

7

### SAA6752HS

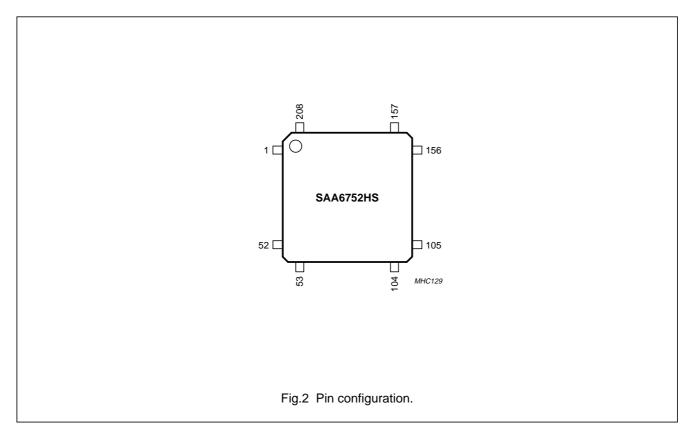

### 6 PINNING

| SYMBOL            | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                                                                                                                            |

|-------------------|-----|-----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SSP</sub>  | 1   | ground                      | _                        | pad ground                                                                                                                                             |

| SDATA1            | 2   | input                       | -                        | I <sup>2</sup> S-bus serial data input port 1 with internal pull-down resistor                                                                         |

| SCLK1             | 3   | input/output                | 4                        | I <sup>2</sup> S-bus serial clock port 1 with internal pull-down resistor                                                                              |

| SWS1              | 4   | input/output                | 4                        | I <sup>2</sup> S-bus word select port 1 with internal pull-down resistor                                                                               |

| V <sub>DDP</sub>  | 5   | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                                                        |

| SDATA2            | 6   | input/output                | 4                        | I <sup>2</sup> S-bus serial data port 2 with internal pull-down resistor                                                                               |

| SCLK2             | 7   | input/output                | 4                        | I <sup>2</sup> S-bus serial clock port 2 with internal pull-down resistor                                                                              |

| SWS2              | 8   | input/output                | 4                        | I <sup>2</sup> S-bus word select port 2 with internal pull-down resistor                                                                               |

| ACLK              | 9   | output                      | 4                        | audio clock output (256f <sub>s</sub> or 384f <sub>s</sub> )                                                                                           |

| V <sub>SSP</sub>  | 10  | ground                      | _                        | pad ground                                                                                                                                             |

| IDQ               | 11  | input                       | -                        | reserved input with internal pull-down resistor; (recommended to connect to pin $V_{\text{SSP}}$ )                                                     |

| YUV0              | 12  | input                       | -                        | video input signal bit 0 (LSB)                                                                                                                         |

| YUV1              | 13  | input                       | _                        | video input signal bit 1                                                                                                                               |

| YUV2              | 14  | input                       | -                        | video input signal bit 2                                                                                                                               |

| YUV3              | 15  | input                       | -                        | video input signal bit 3                                                                                                                               |

| YUV4              | 16  | input                       | _                        | video input signal bit 4                                                                                                                               |

| YUV5              | 17  | input                       | _                        | video input signal bit 5                                                                                                                               |

| YUV6              | 18  | input                       | _                        | video input signal bit 6                                                                                                                               |

| YUV7              | 19  | input                       | _                        | video input signal bit 7 (MSB)                                                                                                                         |

| V <sub>SSP</sub>  | 20  | ground                      | -                        | pad ground                                                                                                                                             |

| HSYNC             | 21  | input                       | _                        | horizontal sync input (video) with internal pull-down resistor                                                                                         |

| VSYNC             | 22  | input                       | -                        | vertical sync input (video) with internal pull-down resistor                                                                                           |

| FID               | 23  | input                       | -                        | video field identification input (odd/even field) with internal pull-down resistor                                                                     |

| VCLK1             | 24  | input                       | -                        | video clock input 1 (27 MHz) with internal pull-down resistor                                                                                          |

| V <sub>SSCO</sub> | 25  | ground                      | -                        | core ground                                                                                                                                            |

| V <sub>SSCO</sub> | 26  | ground                      | -                        | core ground                                                                                                                                            |

| V <sub>DDCO</sub> | 27  | supply                      | -                        | core supply voltage (2.5 V)                                                                                                                            |

| V <sub>DDCO</sub> | 28  | supply                      | -                        | core supply voltage (2.5 V)                                                                                                                            |

| V <sub>DDP</sub>  | 29  | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                                                        |

| VCLK2             | 30  | input                       | -                        | video clock input 2 (27 MHz) with internal pull-down resistor                                                                                          |

| PDOAV             | 31  | 3-state output              | 4                        | parallel stream data output for audio/video identifier                                                                                                 |

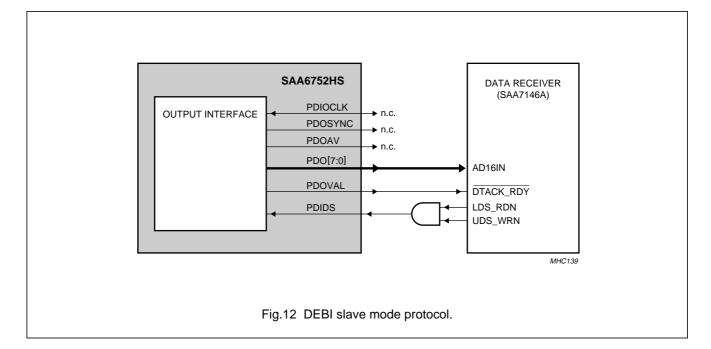

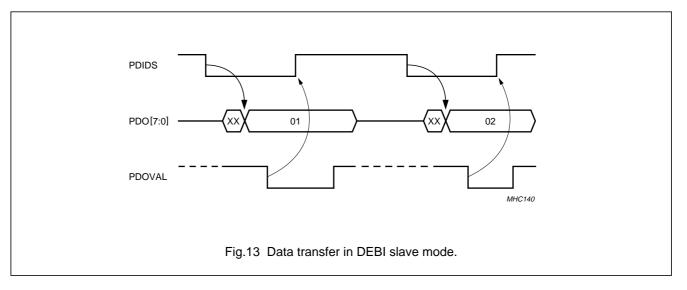

| PDIDS             | 32  | input                       | _                        | parallel stream data input for data strobe [request for packet in<br>Data Expansion Bus Interface (DEBI) slave mode] with internal<br>pull-up resistor |

| PDOSYNC           | 33  | 3-state output              | 4                        | parallel stream data output for packet sync                                                                                                            |

| V <sub>SSP</sub>  | 34  | ground                      | _                        | pad ground                                                                                                                                             |

| PDOVAL            | 35  | 3-state output              | 4                        | parallel stream data valid output with internal pull-up resistor                                                                                       |

| PDO0              | 36  | 3-state output              | 4                        | parallel stream data output bit 0 (LSB)                                                                                                                |

| SYMBOL           | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                                              |

|------------------|-----|-----------------------------|--------------------------|--------------------------------------------------------------------------|

| PDO1             | 37  | 3-state output              | 4                        | parallel stream data output bit 1                                        |

| PDO2             | 38  | 3-state output              | 4                        | parallel stream data output bit 2                                        |

| V <sub>DDP</sub> | 39  | supply                      | -                        | pad ring supply voltage (3.3 V)                                          |

| PDO3             | 40  | 3-state output              | 4                        | parallel stream data output bit 3                                        |

| PDO4             | 41  | 3-state output              | 4                        | parallel stream data output bit 4                                        |

| PDO5             | 42  | 3-state output              | 4                        | parallel stream data output bit 5                                        |

| PDO6             | 43  | 3-state output              | 4                        | parallel stream data output bit 6                                        |

| V <sub>SSP</sub> | 44  | ground                      | -                        | pad ground                                                               |

| PDO7             | 45  | 3-state output              | 4                        | parallel stream data output bit 7 (MSB)                                  |

| PDIOCLK          | 46  | input/output                | 4                        | parallel stream clock input/output                                       |

| I2CADDRSEL       | 47  | input                       | -                        | I <sup>2</sup> C-bus address select input with internal pull-up resistor |

| SD_DQ15          | 48  | input/output                | 8                        | SDRAM data input/output bit 15 (MSB)                                     |

| V <sub>DDP</sub> | 49  | supply                      | -                        | pad ring supply voltage (3.3 V)                                          |

| SD_DQ0           | 50  | input/output                | 8                        | SDRAM data input/output bit 0 (LSB)                                      |

| SD_DQ14          | 51  | input/output                | 8                        | SDRAM data input/output bit 14                                           |

| SD_DQ1           | 52  | input/output                | 8                        | SDRAM data input/output bit 1                                            |

| V <sub>SSP</sub> | 53  | ground                      | _                        | pad ground                                                               |

| SD_DQ13          | 54  | input/output                | 8                        | SDRAM data input/output bit 13                                           |

| SD_DQ2           | 55  | input/output                | 8                        | SDRAM data input/output bit 2                                            |

| SD_DQ12          | 56  | input/output                | 8                        | SDRAM data input/output bit 12                                           |

| V <sub>DDP</sub> | 57  | supply                      | _                        | pad ring supply voltage (3.3 V)                                          |

| SD_DQ3           | 58  | input/output                | 8                        | SDRAM data input/output bit 3                                            |

| SD_DQ11          | 59  | input/output                | 8                        | SDRAM data input/output bit 11                                           |

| SD_DQ4           | 60  | input/output                | 8                        | SDRAM data input/output bit 4                                            |

| SD_DQ10          | 61  | input/output                | 8                        | SDRAM data input/output bit 10                                           |

| V <sub>SSP</sub> | 62  | ground                      | -                        | pad ground                                                               |

| SD_DQ5           | 63  | input/output                | 8                        | SDRAM data input/output bit 5                                            |

| SD_DQ9           | 64  | input/output                | 8                        | SDRAM data input/output bit 9                                            |

| SD_DQ6           | 65  | input/output                | 8                        | SDRAM data input/output bit 6                                            |

| SD_DQ8           | 66  | input/output                | 8                        | SDRAM data input/output bit 8                                            |

| V <sub>DDP</sub> | 67  | supply                      | -                        | pad ring supply voltage (3.3 V)                                          |

| SD_DQ7           | 68  | input/output                | 8                        | SDRAM data input/output bit 7                                            |

| SD_DQM1          | 69  | output                      | 8                        | SDRAM data mask enable output bit 1                                      |

| SD_DQM0          | 70  | output                      | 8                        | SDRAM data mask enable output bit 0 (LSB)                                |

| SD_WE            | 71  | output                      | 8                        | SDRAM write enable output (active LOW)                                   |

| V <sub>SSP</sub> | 72  | ground                      | -                        | pad ground                                                               |

| SD_CAS           | 73  | output                      | 8                        | SDRAM column address strobe output (active LOW)                          |

| SD_CLK           | 74  | output                      | 8                        | SDRAM clock output                                                       |

| SD_RAS           | 75  | output                      | 8                        | SDRAM row address strobe output (active LOW)                             |

| SD_CKE           | 76  | output                      | 8                        | SDRAM clock enable output                                                |

| SYMBOL            | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                              |

|-------------------|-----|-----------------------------|--------------------------|----------------------------------------------------------|

| V <sub>SSCO</sub> | 77  | ground                      | _                        | core ground                                              |

| V <sub>SSCO</sub> | 78  | ground                      | -                        | core and substrate ground                                |

| V <sub>DDCO</sub> | 79  | supply                      | -                        | core supply voltage (2.5 V)                              |

| V <sub>DDCO</sub> | 80  | supply                      | _                        | core supply voltage (2.5 V)                              |

| V <sub>DDP</sub>  | 81  | supply                      | _                        | pad ring supply voltage (3.3 V)                          |

| SD_CS             | 82  | output                      | 8                        | SDRAM chip select output (active LOW)                    |

| SD_A13            | 83  | output                      | 8                        | SDRAM address output bit 13 (bank selection for 64 Mbit) |

| SD_A9             | 84  | output                      | 8                        | SDRAM address output bit 9                               |

| SD_A8             | 85  | output                      | 8                        | SDRAM address output bit 8                               |

| V <sub>SSP</sub>  | 86  | ground                      | -                        | pad ground                                               |

| SD_A11            | 87  | output                      | 8                        | SDRAM address output bit 11 (bank selection for 16 Mbit) |

| SD_A7             | 88  | output                      | 8                        | SDRAM address output bit 7                               |

| SD_A12            | 89  | output                      | 8                        | SDRAM address output bit 12 (bank selection for 64 Mbit) |

| SD_A6             | 90  | output                      | 8                        | SDRAM address output bit 6                               |

| V <sub>DDP</sub>  | 91  | supply                      | _                        | pad ring supply voltage (3.3 V)                          |

| SD_A10            | 92  | output                      | 8                        | SDRAM address output bit 10                              |

| SD_A5             | 93  | output                      | 8                        | SDRAM address output bit 5                               |

| SD_A0             | 94  | output                      | 8                        | SDRAM address output bit 0 (LSB)                         |

| SD_A4             | 95  | output                      | 8                        | SDRAM address output bit 4                               |

| V <sub>SSP</sub>  | 96  | ground                      | _                        | pad ground                                               |

| SD_A1             | 97  | output                      | 8                        | SDRAM address output bit 1                               |

| SD_A3             | 98  | output                      | 8                        | SDRAM address output bit 3                               |

| SD_A2             | 99  | output                      | 8                        | SDRAM address output bit 2                               |

| SD_DQM3           | 100 | output                      | 8                        | reserved (do not connect)                                |

| V <sub>DDP</sub>  | 101 | supply                      | _                        | pad ring supply voltage (3.3 V)                          |

| SD_DQM2           | 102 | output                      | 8                        | reserved (do not connect)                                |

| SD_DQ31           | 103 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ16           | 104 | input/output                | 8                        | reserved (do not connect)                                |

| V <sub>SSP</sub>  | 105 | ground                      | -                        | pad ground                                               |

| SD_DQ30           | 106 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ17           | 107 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ29           | 108 | input/output                | 8                        | reserved (do not connect)                                |

| V <sub>DDP</sub>  | 109 | supply                      | _                        | pad ring supply voltage (3.3 V)                          |

| SD_DQ18           | 110 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ28           | 111 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ19           | 112 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ27           | 113 | input/output                | 8                        | reserved (do not connect)                                |

| V <sub>SSP</sub>  | 114 | ground                      | _                        | pad ground                                               |

| SD_DQ20           | 115 | input/output                | 8                        | reserved (do not connect)                                |

| SD_DQ26           | 116 | input/output                | 8                        | reserved (do not connect)                                |

| SYMBOL            | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                                                                                                   |

|-------------------|-----|-----------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| SD_DQ21           | 117 | input/output                | 8                        | reserved (do not connect)                                                                                                     |

| SD_DQ25           | 118 | input/output                | 8                        | reserved (do not connect)                                                                                                     |

| V <sub>DDP</sub>  | 119 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                               |

| SD_DQ22           | 120 | input/output                | 8                        | reserved (do not connect)                                                                                                     |

| SD_DQ24           | 121 | input/output                | 8                        | reserved (do not connect)                                                                                                     |

| SD_DQ23           | 122 | input/output                | 8                        | reserved (do not connect)                                                                                                     |

| EXTCLK            | 123 | input                       | -                        | 27 MHz external clock input with internal pull-up resistor                                                                    |

| V <sub>SSP</sub>  | 124 | ground                      | -                        | pad ground                                                                                                                    |

| V <sub>SSA</sub>  | 125 | ground                      | _                        | oscillator analog ground                                                                                                      |

| XTALI             | 126 | analog input                | -                        | crystal oscillator input (27 MHz); note 2                                                                                     |

| XTALO             | 127 | analog output               | -                        | crystal oscillator output (27 MHz)                                                                                            |

| V <sub>DDA</sub>  | 128 | supply                      | _                        | oscillator analog supply voltage (2.5 V)                                                                                      |

| V <sub>SSCO</sub> | 129 | ground                      | -                        | core ground                                                                                                                   |

| V <sub>SSCO</sub> | 130 | ground                      | -                        | core ground                                                                                                                   |

| V <sub>DDCO</sub> | 131 | supply                      | _                        | core supply voltage (2.5 V)                                                                                                   |

| V <sub>DDCO</sub> | 132 | supply                      | -                        | core supply voltage (2.5 V)                                                                                                   |

| V <sub>DDP</sub>  | 133 | supply                      | -                        | pad ring supply voltage (3.3 V)                                                                                               |

| TDI               | 134 | input                       | -                        | boundary scan test data input; pin must float or set to HIGH during normal operating; with internal pull-up resistor; note 3  |

| TMS               | 135 | input                       | -                        | boundary scan test mode select; pin must float or set to HIGH during normal operating; with internal pull-up resistor; note 3 |

| ТСК               | 136 | input                       | -                        | boundary scan test clock; pin must be set to LOW during normal operating; with internal pull-up resistor; note 3              |

| TDO               | 137 | 3-state output              | 4                        | boundary scan test data output; pin not active during normal operating; with 3-state output; note 3                           |

| V <sub>SSP</sub>  | 138 | ground                      | -                        | pad ground                                                                                                                    |

| TRST              | 139 | input                       | -                        | test reset input (active LOW), for boundary scan test (with internal pull-up resistor); notes 3 and 4                         |

| CLKOUT            | 140 | output                      | 4                        | 27 MHz system clock output                                                                                                    |

| TEST0             | 141 | input/output                | 4                        | reserved (do not connect)                                                                                                     |

| TEST1             | 142 | input/output                | 4                        | reserved (do not connect)                                                                                                     |

| V <sub>DDP</sub>  | 143 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                               |

| TEST2             | 144 | input/output                | 4                        | reserved (do not connect)                                                                                                     |

| SDA               | 145 | input/open-drain<br>output  | -                        | I <sup>2</sup> C-bus serial data input/output                                                                                 |

| SCL               | 146 | input/open-drain<br>output  | -                        | I <sup>2</sup> C-bus serial clock input/output                                                                                |

| RESET             | 147 | input                       | -                        | reset input (active LOW); with internal pull-up resistor                                                                      |

| V <sub>SSP</sub>  | 148 | ground                      | -                        | pad ground                                                                                                                    |

| RTS               | 149 | output                      | 4                        | reserved (do not connect); Universal Asynchronous<br>Receiver/Transmitter (UART) request to send output (active<br>LOW)       |

| SYMBOL           | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                                                                                                                                         |

|------------------|-----|-----------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS              | 150 | input                       | -                        | reserved (recommended connect to pin V <sub>DDP</sub> ); UART clear to send input; external static memory select input (active LOW); with internal pull-up resistor |

| RXD              | 151 | input                       | -                        | reserved (recommended connect to pin V <sub>DDP</sub> ); UART receive data; internal boot select input; with internal pull-up resistor                              |

| TXD              | 152 | output                      | 4                        | reserved (do not connect); UART transmit data                                                                                                                       |

| V <sub>DDP</sub> | 153 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                                                                     |

| SM_LB            | 154 | input/output                | 4                        | reserved (do not connect)                                                                                                                                           |

| SM_UB            | 155 | input/output                | 4                        | reserved (do not connect)                                                                                                                                           |

| H_IRF            | 156 | 3-state output              | 4                        | host interrupt flag output; with internal pull-up resistor (active LOW)                                                                                             |

| V <sub>SSP</sub> | 157 | ground                      | _                        | pad ground                                                                                                                                                          |

| SM_OE            | 158 | output                      | 4                        | reserved (do not connect); static memory output enable output (active LOW)                                                                                          |

| SM_A9            | 159 | output                      | 4                        | reserved (do not connect); static memory address output bit 9                                                                                                       |

| SM_A10           | 160 | output                      | 4                        | reserved (do not connect); static memory address output bit 10                                                                                                      |

| V <sub>DDP</sub> | 161 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                                                                     |

| SM_A8            | 162 | output                      | 4                        | reserved (do not connect); static memory address output bit 8                                                                                                       |

| SM_A11           | 163 | output                      | 4                        | reserved (do not connect); static memory address output bit 11                                                                                                      |

| SM_A7            | 164 | output                      | 4                        | reserved (do not connect); static memory address output bit 7                                                                                                       |

| SM_A12           | 165 | output                      | 4                        | reserved (do not connect); static memory address output bit 12                                                                                                      |

| V <sub>SSP</sub> | 166 | ground                      | _                        | pad ground                                                                                                                                                          |

| SM_A6            | 167 | output                      | 4                        | reserved (do not connect); static memory address output bit 6                                                                                                       |

| SM_A13           | 168 | output                      | 4                        | reserved (do not connect); static memory address output bit 13                                                                                                      |

| SM_A5            | 169 | output                      | 4                        | reserved (do not connect); static memory address output bit 5                                                                                                       |

| SM_A14           | 170 | output                      | 4                        | reserved (do not connect); static memory address output bit 14                                                                                                      |

| V <sub>DDP</sub> | 171 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                                                                                     |

| SM_WE            | 172 | output                      | 4                        | reserved (do not connect); static memory write enable output (active LOW)                                                                                           |

| SM_D7            | 173 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 7 with internal pull-down resistor                                                                   |

| SM_D8            | 174 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 8 with internal pull-down resistor                                                                   |

| SM_D6            | 175 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 6 with internal pull-down resistor                                                                   |

| V <sub>SSP</sub> | 176 | ground                      | _                        | pad ground                                                                                                                                                          |

| SM_D9            | 177 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 9 with internal pull-down resistor                                                                   |

| SM_D5            | 178 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 5 with internal pull-down resistor                                                                   |

| SM_D10           | 179 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 10 with internal pull-down resistor                                                                  |

| SYMBOL            | PIN | INPUT/OUTPUT <sup>(1)</sup> | I <sub>max</sub><br>(mA) | DESCRIPTION                                                                                              |

|-------------------|-----|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|

| SM_D4             | 180 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 4 with internal pull-down resistor        |

| V <sub>SSCO</sub> | 181 | ground                      | -                        | internal pre-driver and substrate ground                                                                 |

| V <sub>SSCO</sub> | 182 | ground                      | -                        | core ground                                                                                              |

| V <sub>DDCO</sub> | 183 | supply                      | -                        | core supply voltage (2.5 V)                                                                              |

| V <sub>DDCO</sub> | 184 | supply                      | -                        | internal pre-driver supply voltage (2.5 V)                                                               |

| V <sub>DDP</sub>  | 185 | supply                      | -                        | pad ring supply voltage (3.3 V)                                                                          |

| SM_D11            | 186 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 11 with internal pull-down resistor       |

| SM_D3             | 187 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 3 with internal pull-down resistor        |

| SM_D12            | 188 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 12 with internal pull-down resistor       |

| SM_D2             | 189 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 2 with internal pull-down resistor        |

| V <sub>SSP</sub>  | 190 | ground                      | -                        | pad ground                                                                                               |

| SM_D13            | 191 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 13 with internal pull-down resistor       |

| SM_D1             | 192 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 1 with internal pull-down resistor        |

| SM_D14            | 193 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 14 with internal pull-down resistor       |

| SM_D0             | 194 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 0 (LSB) with internal pull-down resistor  |

| V <sub>DDP</sub>  | 195 | supply                      | _                        | pad ring supply voltage (3.3 V)                                                                          |

| SM_D15            | 196 | input/output                | 4                        | reserved (do not connect); static memory data input/output bit 15 (MSB) with internal pull-down resistor |

| SM_CS3            | 197 | output                      | 4                        | reserved (do not connect); static memory chip select output for external ROM or RAM (active LOW)         |

| SM_A4             | 198 | output                      | 4                        | reserved (do not connect); static memory address output bit 4                                            |

| SM_A3             | 199 | output                      | 4                        | reserved (do not connect); static memory address output bit 3                                            |

| V <sub>SSP</sub>  | 200 | ground                      | _                        | pad ground                                                                                               |

| SM_A2             | 201 | output                      | 4                        | reserved (do not connect); static memory address output bit 2                                            |

| SM_A15            | 202 | output                      | 4                        | reserved (do not connect); static memory address output bit 15                                           |

| SM_A1             | 203 | output                      | 4                        | reserved (do not connect); static memory address output bit 1                                            |

| SM_A16            | 204 | output                      | 4                        | reserved (do not connect); static memory address output bit 16                                           |

| V <sub>DDP</sub>  | 205 | supply                      | -                        | pad ring supply voltage (3.3 V)                                                                          |

| SM_A0             | 206 | output                      | 4                        | reserved (do not connect); static memory address output bit 0 (LSB)                                      |

| SM_A17            | 207 | output                      | 4                        | reserved (do not connect); static memory address output bit 17 (MSB)                                     |

| SM_CS0            | 208 | output                      | 4                        | reserved (do not connect)                                                                                |

### SAA6752HS

### Notes

- 1. All input pins, input/output pins (in input mode), output pins (in 3-state mode) and open-drain output pins are limited to 3.3 V.

- 2. If used with external clock source the input voltage has to be limited to 2.5 V.

- 3. In accordance with the *"IEEE 1149.1"* standard.

- 4. Special function of pin TRST:

- a) For board designs without boundary scan implementation, pin TRST must be connected to ground.

- b) Pin TRST provides easy initialization of the internal BST circuit. By applying a LOW level it can be used to force the internal Test Access Port (TAP) controller to the Test-Logic-Reset state (normal operating) immediately.

### Product specification

SAA6752HS

# MPEG-2 video and MPEG-audio/AC-3 audio encoder with multiplexer

### 7 FUNCTIONAL DESCRIPTION

### 7.1 System operation

### 7.1.1 GENERAL

The SAA6752HS has a multi-processor architecture. The different processing and control modules are not locked to each other but run independently within the limits of the global scheduling. The data transfer between the processing units is carried out via FIFO memories or the external SDRAM. The device is configured and the operation modes are selected via the I<sup>2</sup>C-bus.

### 7.1.2 OPERATING MODES

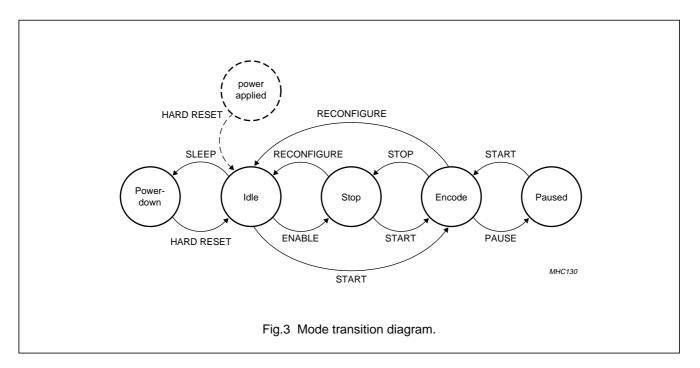

There are five operating modes:

Idle. This mode is set after applying a hard reset (i.e. on power-up). In this mode the SAA6752HS can be initialized by the host to the required configuration. Video and audio processing is disabled. A hard reset always resets the SAA6752HS configuration parameters back to the default states.

- 2. **Stop.** In Stop mode, the video and audio input processing is enabled but the multiplexer output remains disabled. It is possible to read status information on the input video and audio signals via the I<sup>2</sup>C-bus. The SAA6752HS initialization settings cannot be modified, except to some specific dynamic encoding parameters (i.e. bit rate setting).

- 3. **Encode.** In this mode, the multiplexer output is enabled. Like Stop mode, only dynamic encoding parameters can be modified in this mode.

- 4. **Paused.** This mode allows the SAA6752HS to make seamless transitions. Restarting from Paused mode will generate a stream output with sequential time stamps and MPEG buffer model content.

- 5. **Power-down.** In this mode, the internal clock is disabled, sending the SAA6752HS into a (non-functional) power saving state. A hard reset will re-initialize the SAA6752HS.

SAA6752HS

# MPEG-2 video and MPEG-audio/AC-3 audio encoder with multiplexer

### 7.1.3 MODE TRANSITION COMMANDS

There are seven mode transition commands:

- 1. **SOFT RESET.** Like a hard reset, a soft reset can be applied in any mode, setting the SAA6752HS back to Idle mode and resetting all configuration parameters back to the default settings.

- RECONFIGURE. This command sets the SAA6752HS back to Idle mode without resetting the configuration parameters back to the default settings.

- 3. **ENABLE.** This transition sets Stop mode, enabling the video and audio input processing.

- 4. **START.** This transition sets Encode mode, enabling the multiplexer stream output. Note that if the SAA6752HS is commanded to start from the Idle mode, then the internal transition is via the Stop mode.

- 5. **STOP.** This command will disable the multiplexer stream output, setting the SAA6752HS to Stop mode. The current GOP and/or audio frame is completed and an end of sequence bit appended to the stream.

- 6. **PAUSE.** A PAUSE transition will cause the multiplexer to complete the current GOP and/or audio frame but no end of sequence bit is appended. The current MPEG buffer model contents are saved to provide a seamless transition on START.

- 7. **SLEEP.** This mode disables the internal clock.

- 8. FORCED RECONFIGURE. A STOP command whilst in the Encode mode will not work in case the video or audio input signal is interrupted, because for stopping, the SAA6752HS tries to finish the current GOP. The forced reconfigure command allows a mode transition back to the Idle state, without losing the actual configuration settings. The forced reconfiguration performs a soft reset and the automatic internal reprogramming of the I<sup>2</sup>C-bus registers. The forced reconfiguration will take about 200 ms; during the forced reconfiguration all register values will change to their default values before they are reprogrammed. Please note that outputs, which can be switched to high-impedance or to input mode, will not be active during the forced reconfiguration.

The SAA6752HS is not able to process any other commands during mode transitions. In this event, a get running mode request will return a busy flag. The completion of a mode transition can also be flagged as an event using the host interrupt pin.

### 7.2 Digital video input

### 7.2.1 GENERAL

The video front-end processes an *"ITU-R BT.601/605"* compliant video stream for conversion to 4 : 2 : 0 format (MP@ML). It includes synchronization, digital video signal processing through several filters, subsampling, sliced/raw VBI data handling, and SDRAM address generation.

The video interface is designed for use with Philips SAA7114 digital multi-standard decoder or similar video decoders. The input interface accepts a digital video input stream according to *"ITU-R-BT.601"*. 625 lines standard at 50 Hz and 720 pixels by 576 lines as well as 525 lines at 60 Hz and 720 pixels by 480 lines are covered. The video synchronization may either follow *"ITU-R-BT.656"* recommendation or can also be supplied by external signals (HSYNC, VSYNC and FID). The formatter module performs a colour conversion from 4 : 2 : 2 to 4 : 2 : 0 format. Optionally, also SIF progressive downscaling and 2/3D1, 1/2D1 downscaling may be activated.

The SAA6752HS supports non-standard features of the SAA711x series of video input processors, such as hard-wired external synchronization signals (2 and 3-wire sync), special VCR playback signal streams (IEC 756 subset for VCR playback and still pictures), extraction of sliced data from the input video stream.

### 7.2.2 VIDEO FRONT-END CONFIGURATION OPTIONS

The following configuration options can be selected from the host:

- VIDEO INPUT PORT SELECTION. Two input clock pins are selectable.

- VIDEO INPUT FORMAT. 525 or 625-line formats can be selected.

- VIDEO SYNC FORMAT. Various combinations and polarities of HSYNC, VSYNC and Field Information (FID) can be selected as the source of sync signal processing.

- VIDEO FILTER SETTINGS. Noise pre-filter and horizontal filters can be enabled and, if the default coefficients are not suitable for an application, new coefficients can be set.

- VIDEO FORMAT CONVERSION. Selection of conversion from D1 to 1/2D1, 2/3D1 or SIF progressive downscaling.

- VBI DATA EXTRACTION. VBI data extraction of WSS or CC data can be enabled.

#### 7.2.3 VIDEO ENCODER STATUS INFORMATION

The following configuration option can be selected from the host:

• VBI DATA: WSS and CC data can be read back via the I<sup>2</sup>C-bus.

### 7.2.4 DATA INPUT FORMAT

### 7.2.4.1 Interface definition

The data input interface uses 13 pins, all of which are inputs (see Table 1). Pins YUV0 to YUV7 carry video and synchronization data and 3 pins are reserved for control purposes. Two separate clock inputs allow two different signal sources to be used. The input clock can be asynchronous to the SAA6752HS system clock.

| Table 1 | List of pins data | input port |

|---------|-------------------|------------|

|---------|-------------------|------------|

| PIN            | DESCRIPTION                                  |

|----------------|----------------------------------------------|

| YUV0 to YUV7   | video input signal<br>(synchronous to VCLK)  |

| FID            | odd/even field identification signal; note 1 |

| HSYNC          | horizontal synchronization signal; note 1    |

| VSYNC          | vertical synchronization signal; note 1      |

| VCLK1 or VCLK2 | video clock signal (from source 1 or 2)      |

### Note

1. In ITU-T 656 mode sync signals are embedded in the video data input stream. The external sync signals are not used.

#### 7.2.5 VIDEO SIGNAL PROCESSING

### 7.2.5.1 Acquisition of video data

Data is latched with the incoming video clock to provide robust data capture. Video clock and data is unlocked to the internal system clock therefore a clock domain bridge is used. This is performed by oversampling of video clock and data with 108 MHz.

### 7.2.5.2 Sync decoding and filtering

To allow selection of the right portion of the video input stream, synchronization signals from the stream are

### SAA6752HS

recognized by a sync decoder. This checks the incoming field (FID), vertical sync and horizontal sync. It is possible to select either 'internal synchronization' (which means that SAV/EAV codes in the ITU 601/656 video streams are used) or externally applied hardware synchronization signals (which are given by the video input processor). In the latter case, 3 pin or 2 pin (V-sync and H-sync only) synchronization can be used.

Using 2 pin synchronization, the FID information is given by the timing of the transition of the V-sync. If a Vertical Blanking Interval (VBI) starts during H-sync, the next field will be the top field, otherwise it will be the bottom field.

A sync filter is used to inhibit sync signal triggering if an incorrect number of pixels or lines has been input. It also checks for the correct consecutive fields. The filter works on three different levels. An H-sync is only accepted after a predefined number of video cycles, a V-sync is only accepted after a programmed number of lines and a field is only accepted if top field follows bottom field or vice versa.

### 7.2.5.3 Horizontal and vertical shift

This function is intended for correction in synchronization of external sync signals if incorrectly timed. The amount of shift is programmable via the I<sup>2</sup>C-bus.

### 7.2.5.4 SAV/EAV decoder

A SAV/EAV decoder extracts the F, V and H bits from the video timing reference code. The decoder evaluates the protection bits to be able to correct one bit errors within the code word. If multiple bit errors are detected, the protection bits are ignored and the field (F), vertical sync (V) and horizontal sync (H) bits are directly extracted from the code.

### 7.2.5.5 Video format conversion

The SAA6752HS converts the input video input signal to the formats defined in Table 2 controlled by the  $l^2C$ -bus command. A 4 : 2 : 2 to 4 : 2 : 0 colour conversion is performed as this is a pre-requisite of MPEG MP@ML encoding.

| MODE  | PICTURE FORMAT<br>(PIXEL/LINES) |  |  |  |

|-------|---------------------------------|--|--|--|

| D1    | 720                             |  |  |  |

| 2/3D1 | 480                             |  |  |  |

| 1/2D1 | 352; note 1                     |  |  |  |

| SIF   | 352; notes 1 and 2              |  |  |  |

### Table 2 Format conversion

#### Notes

- 1. The 8 pixels at the right edge of the scaled picture are not encoded.

- 2. Top field only.

### 7.2.6 VIDEO FILTERING

### 7.2.6.1 Adaptive mean filter

The SAA6752HS uses an adaptive mean filter. There are three different filter modes that can be selected: median, averaging or no filter.

The median algorithm provides better noise performance and is well suited to suppress single noise spikes without degrading the signal edges. The averaging algorithm is a standard low-pass filter so has greater impact on signal edges.

The default threshold and gain coefficients of this filter can be overwritten via the  $l^2C$ -bus to allow user optimization for different applications.

### 7.2.6.2 Horizontal pre-filter/decimation filter

There is a horizontal filter for Y and C and this can operate as a pre-filter or decimation filter. It is a symmetrical FIR filter with up to 8 coefficients programmable via the  $I^2C$ -bus.

### 7.2.6.3 Vertical chrominance filtering

For 4 : 2 : 2 to 4 : 2 : 0 conversion, vertical filtering and subsampling of the chrominance is performed. The sequence of coefficients is mirrored in top and bottom field. This generates the right phases of the chrominance samples between the luminance samples (a non co-sited sampling scheme).

### 7.2.7 VBI DATA EXTRACTION

The SAA6752HS supports the extraction of WSS and CC data using two independent VBI data extractor modules. The data is available via the  $I^2$ C-bus.

The following VBI data formats are supported: Closed Caption (CC525 and CC625) and Wide Screen Signalling (WSS525 and WSS625). For CC525, CC625 and WSS625 the sliced data from a video input processor (e.g. SAA7114, SAA7115 or SAA7118) are extracted from the digital video input signal and can be read via the I<sup>2</sup>C-bus. For WSS525 an internal data slicer is available which slices the oversampled raw data, which are delivered by the video input processor. The extracted WSS525 signal can be read via the I<sup>2</sup>C-bus.

Optionally the automatic insertion of extracted Closed Caption data into the user data area of a video stream is possible (for details see Section 7.3.8).

### 7.3 Video compression

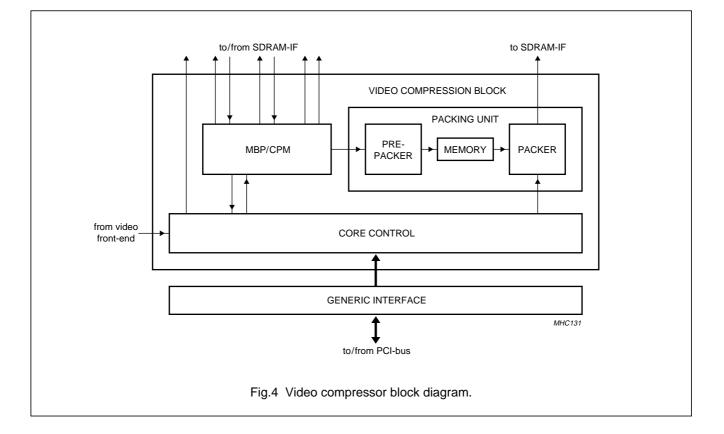

### 7.3.1 GENERAL

Compression of video data is performed by the video compressor block; see Fig.4. The input to this block is the uncompressed video information pre-processed by the video front-end and stored in external SDRAM memory. The output is a compressed video stream, compliant to MPEG-2 Video Elementary Stream (VES) up to slice level. Controlling information (for example, quantizer step size) as well as the bit stream for higher layers of the VES is generated by the embedded MIPS<sup>®</sup> processor of the SAA6752HS.

The video compressor contains several subblocks. The MacroBlock Processor (MBP) performs generation of video ES on macroblock level. Controlling parameters for this task and MB headers as well as slice headers are generated by the core control subblock. Bitstream formatting and concatenation of MBP bitstream and header information is done by the subblocks pre-packer and packer.

#### 7.3.2 VIDEO ENCODER CONFIGURATION OPTIONS

The following configuration options can be selected from the host:

- VIDEO COMPRESSION SETTINGS. I, IP and IPB encoding with various GOP structures can be selected.

- ENCODER BIT RATE. The bit rate for variable bit rate or constant bit rate modes can be programmed using bit rate and quantization control parameters. These parameters can be adjusted whilst encoding, not just set at initialization.

- ENCODER PERFORMANCE TUNING. The ability for the user to tune encoding performance is provided by allowing control of adaptive quantization depth. Also the SAA6752HS allows download of new quantizer matrix contents.

#### 7.3.3 VIDEO ENCODER STATUS INFORMATION

The following status information is available to the host:

• CURRENT ENCODER BIT RATE. The actual encoded bit rate, as number of bytes per GOP, is available allowing the use of constrained variable bit rate algorithms to fine tune the encoding efficiency.

### 7.3.4 GOP STRUCTURE

The programmable GOP structure features a reference frame distance (M) up to 3, and a GOP length (N) of up to 19. Supported structures are real closed GOP(M,N) and backward predicted closed GOP(M,N). For the use of B-frames in D1 and 2/3D1 mode a 64 Mbit SDRAM is needed.

In D1 mode, B-frames will be unidirectional. Backward predicted closed GOPs may have the first one (M = 2) or two (M = 3) B-frames referenced inside the GOP dependent on the I<sup>2</sup>C-bus register settings. This is intended for editable applications as GOPs are independent of each other. Non-editable GOPs allow the first one (M = 1) or two (M = 2) B-frames to be referenced to the P-frame in the previous GOP. This is a non-editable format but has optimum encoding efficiency. This structure is sometimes called an open GOP. The first one (M = 1) or two (M = 2) B-frames in the first GOP of a sequence are always forced backwards predicted.

| GOP        | R   | EFERENC | E FRAME DI            | STANCE (M)             |

|------------|-----|---------|-----------------------|------------------------|

| LENGTH (N) | 0   | 1       | 2                     | 3                      |

| 1          | I   | (1)     | (1)                   | (1)                    |

| 2          | (1) | IP      | (1)                   | (1)                    |

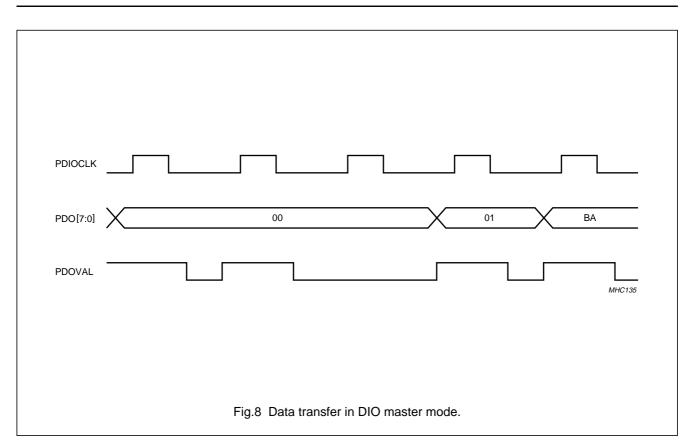

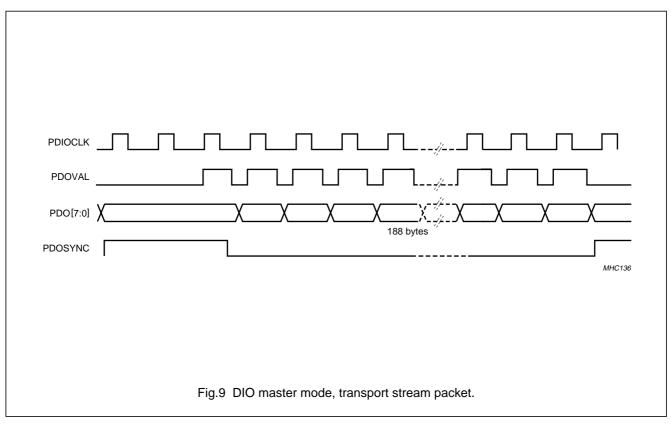

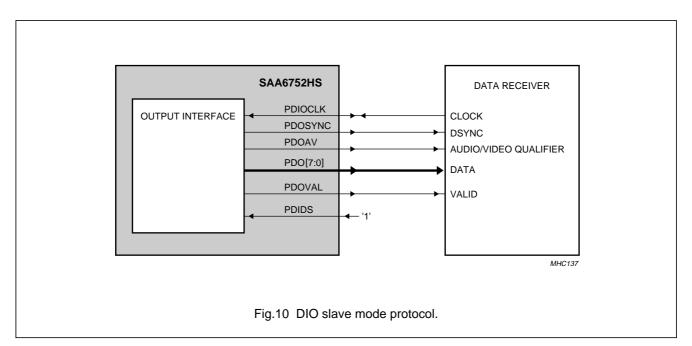

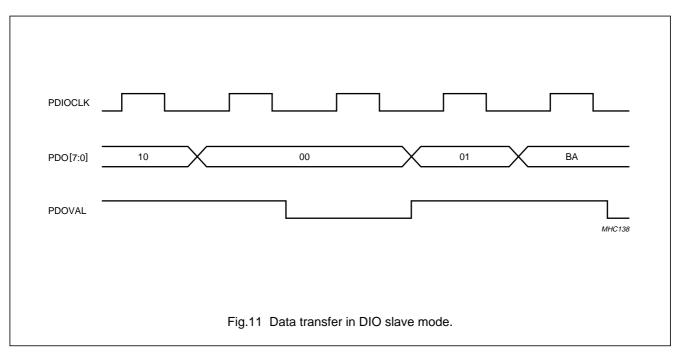

| 3          | (1) | IPP     | IBP <sup>(2)</sup>    | (1)                    |